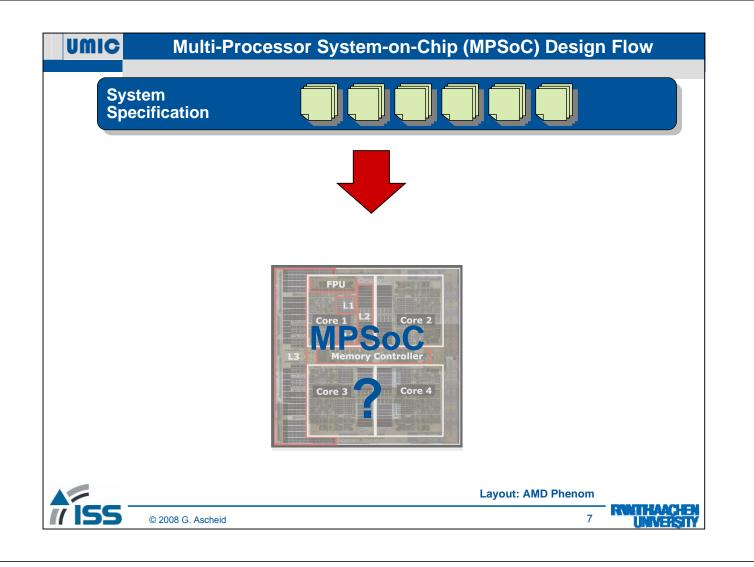

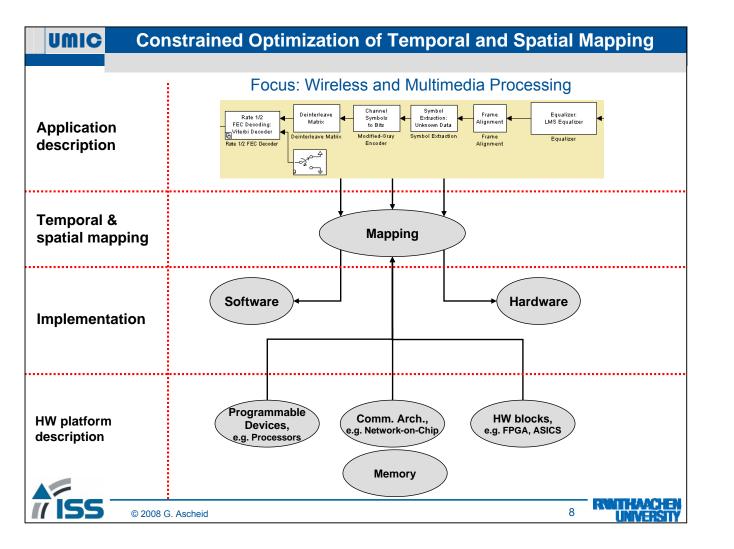

### MPSoC Design Space Exploration Framework

Gerd Ascheid RWTH Aachen University, Germany

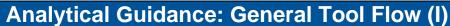

## <image><section-header><section-header><image><image><image><image><image><list-item><list-item><list-item>

5

1/155

© 2008 G. Ascheid

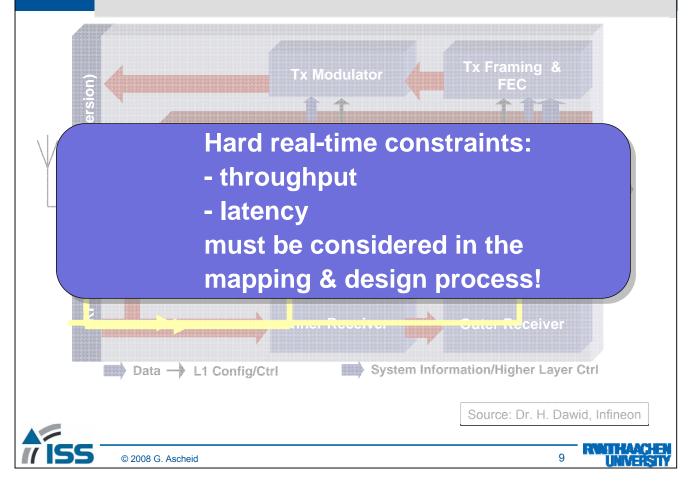

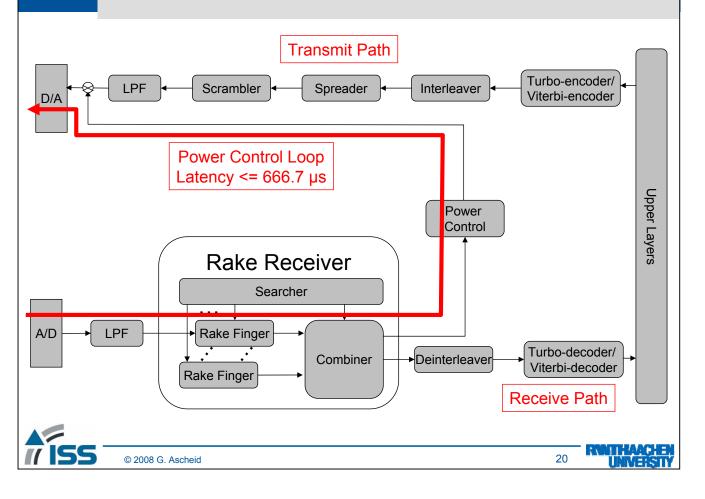

### **Physical Layer Processing**

10

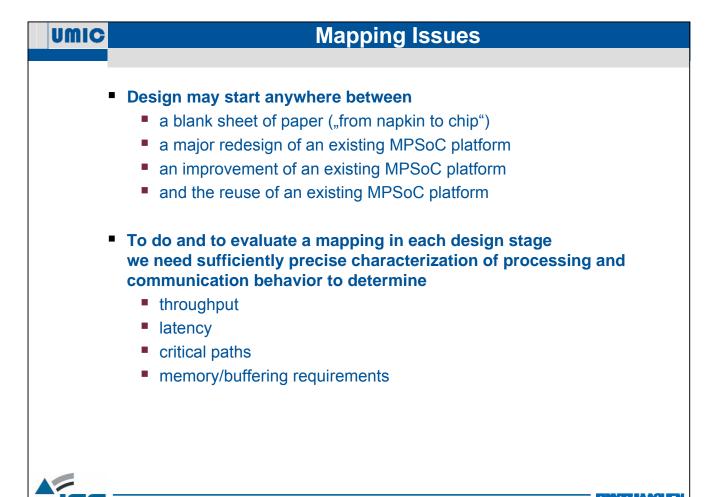

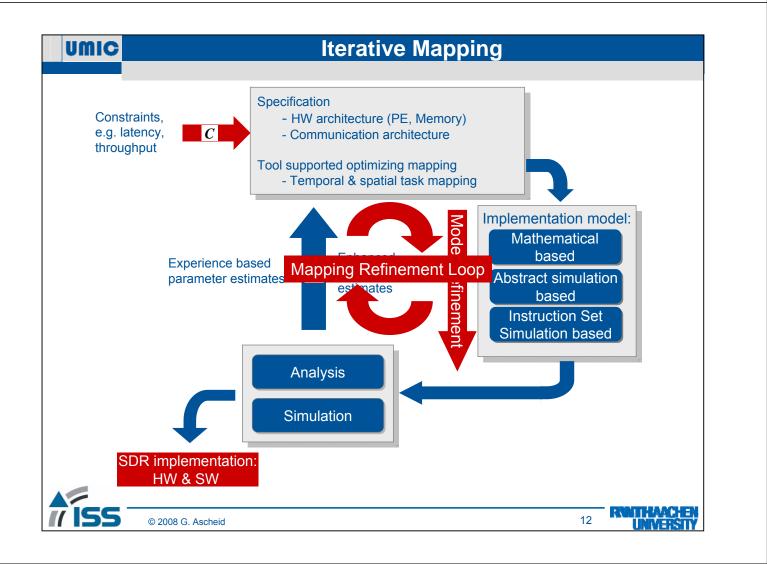

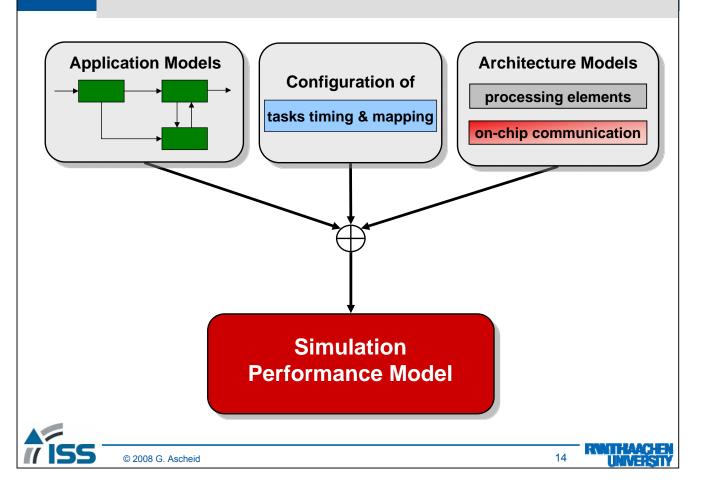

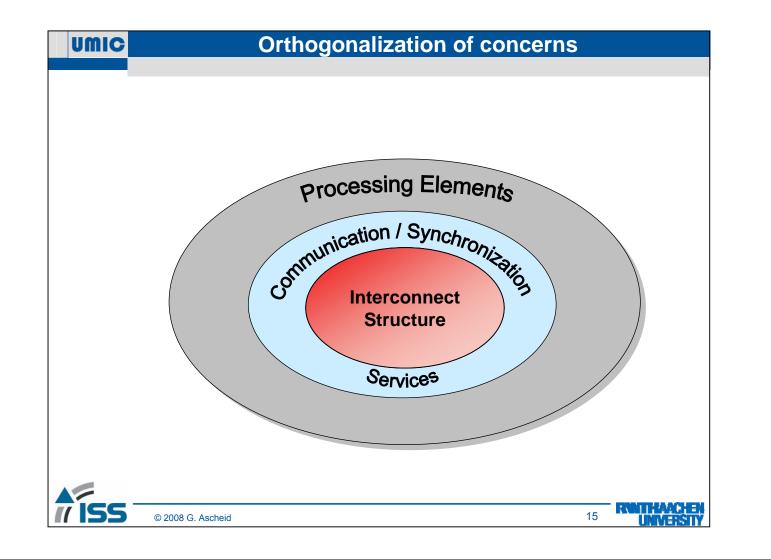

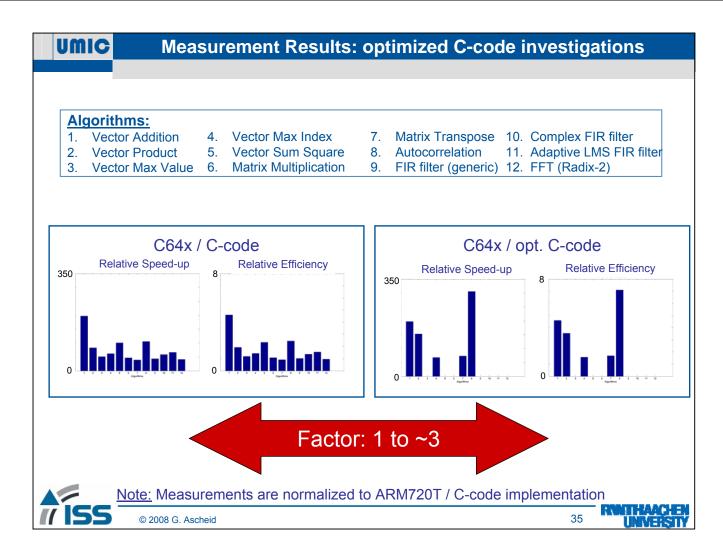

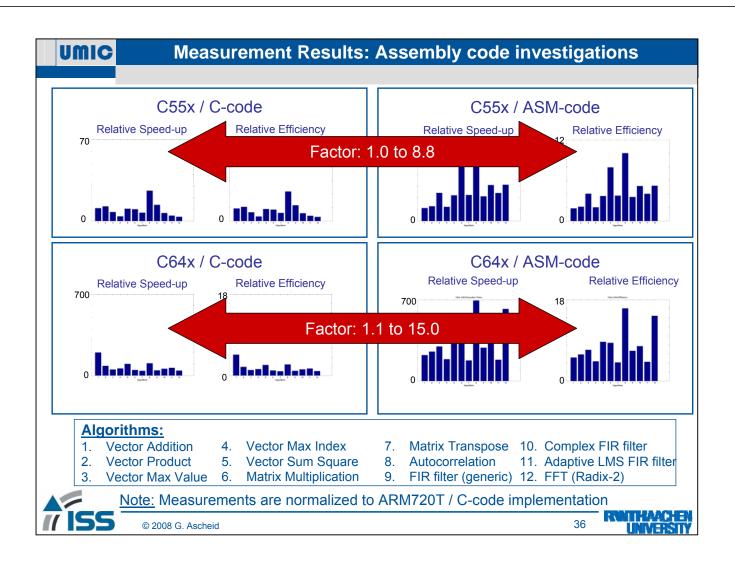

# UMIC Performance Estimation Performance data and/or estimates depend on characterization approach for processing and communication behaviour • Coding style of software:<br/>from generic C model to assembly code optimized for architecture • Modeling style for processing elements • Communication and memory architecture • due to interaction of communication of parallel executed tasks actual performance can only be determined after mapping (⇔ simulation!?) Suggested approach: Iterative mapping at each design stage

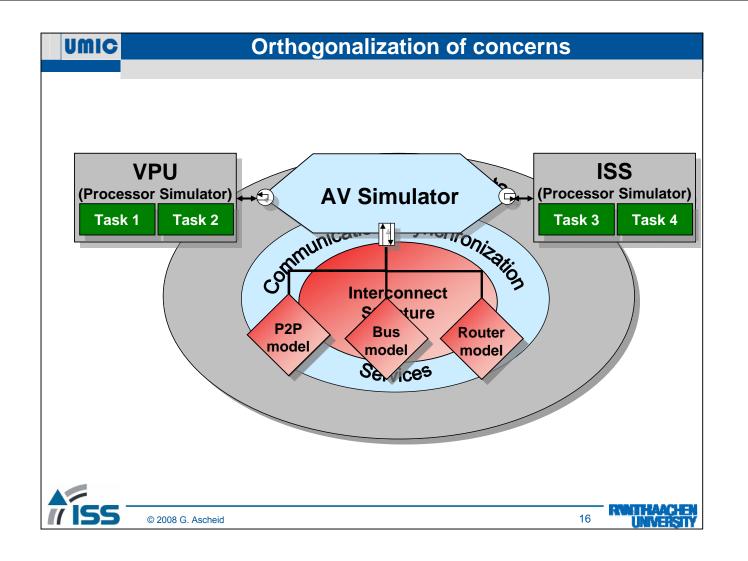

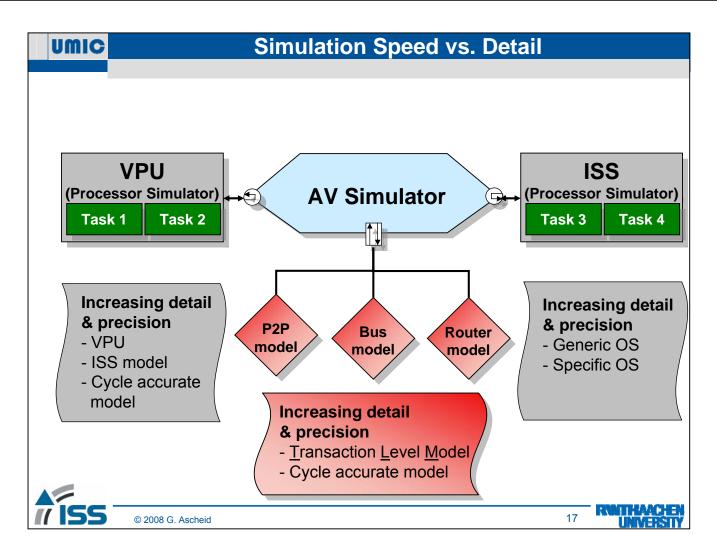

### **UMIC** Simulation Based on Virtual Architecture Mapping

UMIC

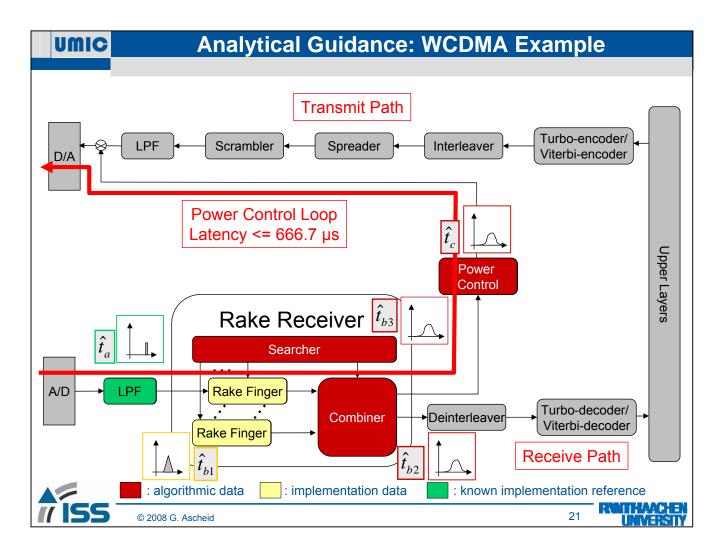

### Analytical Guidance: WCDMA Example

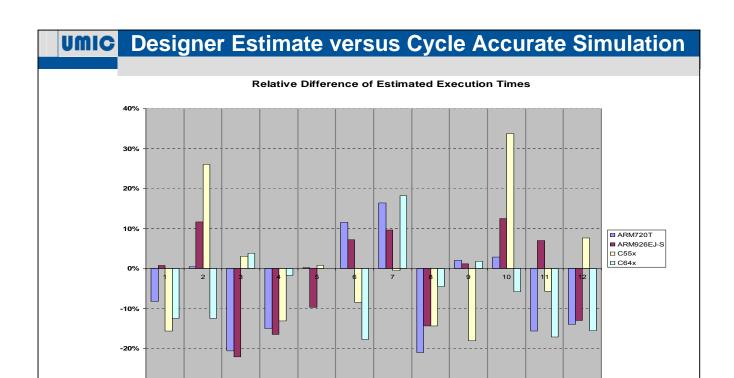

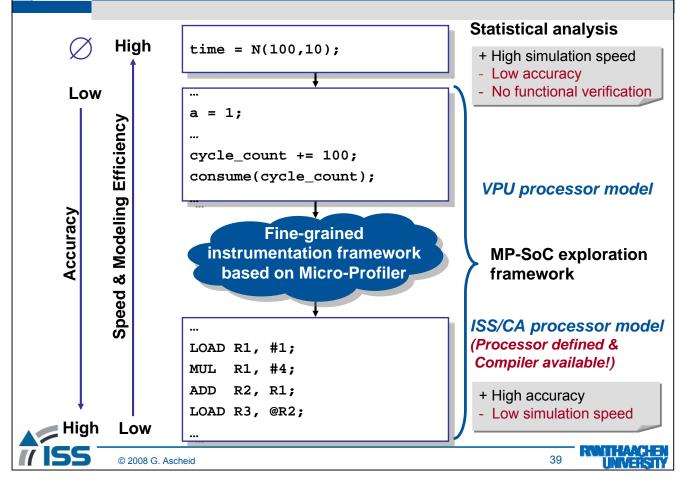

### Mix of Estimation Methods Why is it important to support seamless use of different timing estimation methods? Because of the imprecision of C-code based performance estimates a designer's guess may be more precise than a functional C-code based estimate there is efficient assembler code for key processing algorithms with known execution timing behavior

34

|  | Algorithms: |                   |    |                       |    |                      |     |                         |  |  |  |

|--|-------------|-------------------|----|-----------------------|----|----------------------|-----|-------------------------|--|--|--|

|  | 1.          | Vector Addition   | 4. | Vector Max Index      | 7. | Matrix Transpose     | 10. | Complex FIR filter      |  |  |  |

|  | 2.          | Vector Product    | 5. | Vector Sum Square     | 8. | Autocorrelation      | 11. | Adaptive LMS FIR filter |  |  |  |

|  | 3.          | Vector Max Value  | 6. | Matrix Multiplication | 9. | FIR filter (generic) | 12. | FFT (Radix-2)           |  |  |  |

|  | 55          | © 2008 G. Ascheid |    |                       |    |                      |     | 37 <b>RINTHAACHEN</b>   |  |  |  |

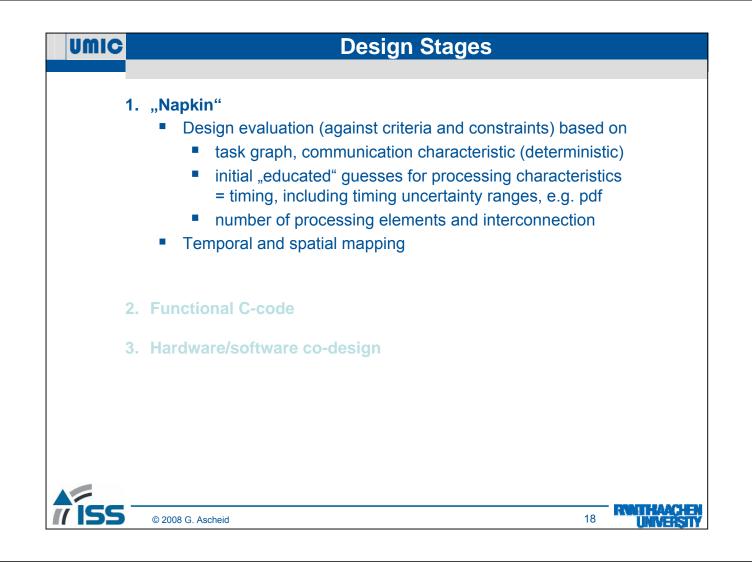

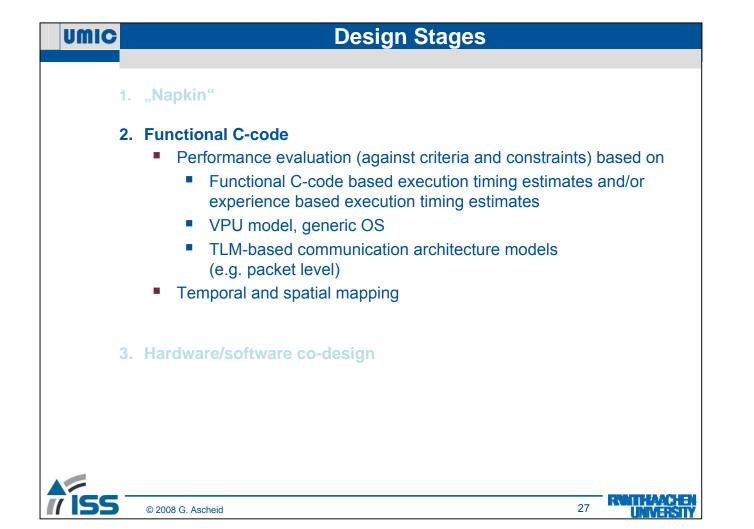

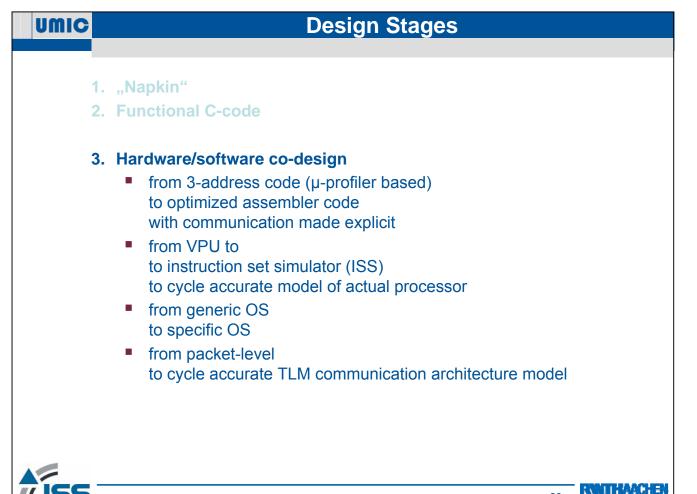

**Design Stages**

1. "Napkin"

-30%

UMIC

- 2. Functional C-code

- 3. Hardware/software co-design

### 4. Final design

- Optimized C and assembler code

- Cycle Accurate model of actual processor

- Specific OS

- Cycle accurate TLM communication architecture model

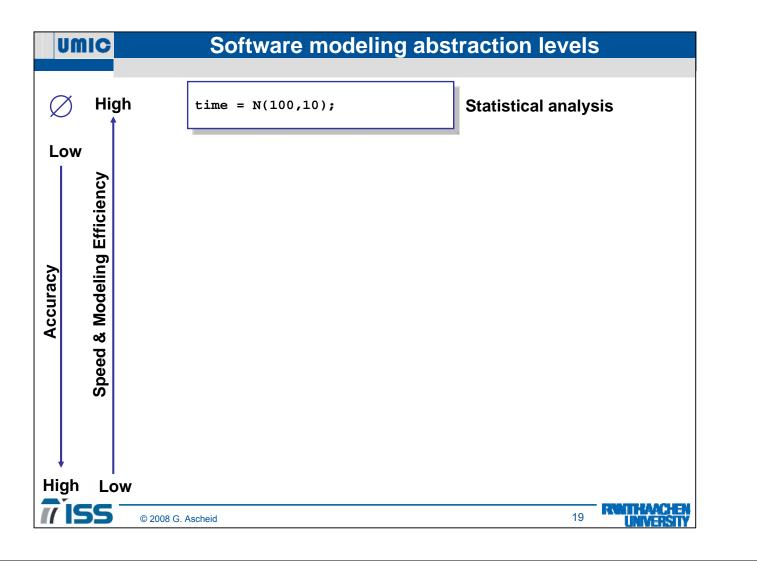

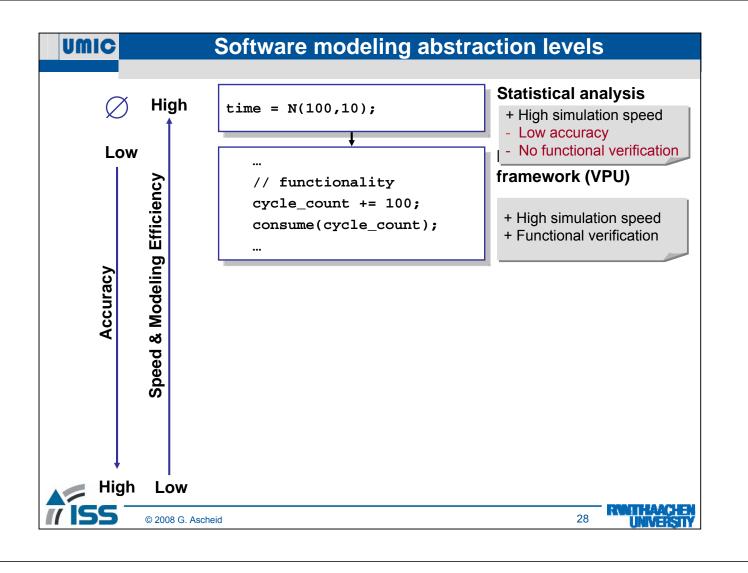

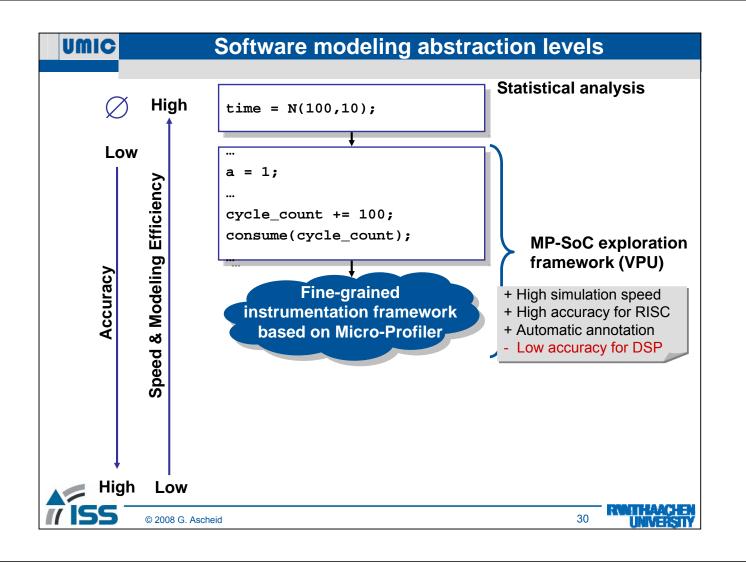

### Software modeling abstraction levels

### **Design Stages**

1. "Napkin"

UMIC

**UMIC**

- 2. C-based simulation

- 3. Hardware/software co-design

- 4. Final design verified:

Pass design to layout team and have a drink or two ...

| UMIC | Summary & Outlook                                                                                          |    |            |  |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------|----|------------|--|--|--|--|--|--|--|

|      |                                                                                                            |    |            |  |  |  |  |  |  |  |

| -    | Summary                                                                                                    |    |            |  |  |  |  |  |  |  |

|      | <ul> <li>Analytically guided design space exploration<br/>and optimized design refinement</li> </ul>       |    |            |  |  |  |  |  |  |  |

|      | <ul> <li>Seamless design flow from high level analysis<br/>to final implementation</li> </ul>              |    |            |  |  |  |  |  |  |  |

|      | <ul> <li>Seamless mixing of different processing<br/>and communication characterization methods</li> </ul> |    |            |  |  |  |  |  |  |  |

| •    | Future work                                                                                                |    |            |  |  |  |  |  |  |  |

|      | Define                                                                                                     |    |            |  |  |  |  |  |  |  |

|      | performance requirement specification method<br>for functional models and                                  |    |            |  |  |  |  |  |  |  |

|      | <ul> <li>feature description for processing elements<br/>and communication architectures</li> </ul>        |    |            |  |  |  |  |  |  |  |

|      | to support tool based mapping                                                                              |    |            |  |  |  |  |  |  |  |

|      | <ul> <li>Mapping tool</li> </ul>                                                                           |    |            |  |  |  |  |  |  |  |

|      | © 2008 G. Ascheid                                                                                          | 42 | RNNTHAACHE |  |  |  |  |  |  |  |